- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT821034DNG (IDT, Integrated Device Technology Inc)IC PCM CODEC QUAD MPI 52-PQFP

14

INDUSTRIAL TEMPERATURE RANGE

IDT821034 QUAD PCM CODEC WITH PROGRAMMABLE GAIN

TIMING CHARACTERISTICS

Clock

Parameter

Description

Min

Typ

Max

Units

Test Conditions

t1

BCLK Duty Cycle

40

60

%

BCLK = 512 kHz to 8.192 MHz

t2

BCLK Rise and Fall Time

15

ns

BCLK = 512 kHz to 8.192 MHz

t3

MCLK Duty Cycle

40

60

%

MCLK = 2.048 MHz, 4.096 MHz or 8.192 MHz

t4

MCLK Rise and Fall Time

15

ns

MCLK = 2.048 MHz, 4.096 MHz or 8.192 MHz

t5

CCLK Rise and Fall Time

15

ns

CCLK ≤ 8.192 MHz

Transmit

Parameter

Description

Min

Typ

Max

Units

Test Conditions

t11

Data Enabled Delay Time

25

ns

CLOAD = 100 pF

t12

Data Delay Time from BCLK

25

ns

CLOAD = 100 pF

t13

Data Float Delay Time

3

8

ns

CLOAD = 0 pF

t14

Frame sync Hold Time

25

ns

t15

Frame sync High Setup Time

25

ns

t16

TSX Enable Delay Time

25

ns

CLOAD = 100 pF

t17

TSX Disable Delay Time

25

ns

CLOAD = 100 pF

t21

Receive Data Setup Time

30

ns

t22

Receive Data Hold Time

15

ns

Note: Timing parameter t12 is referenced to a high-impedance state.

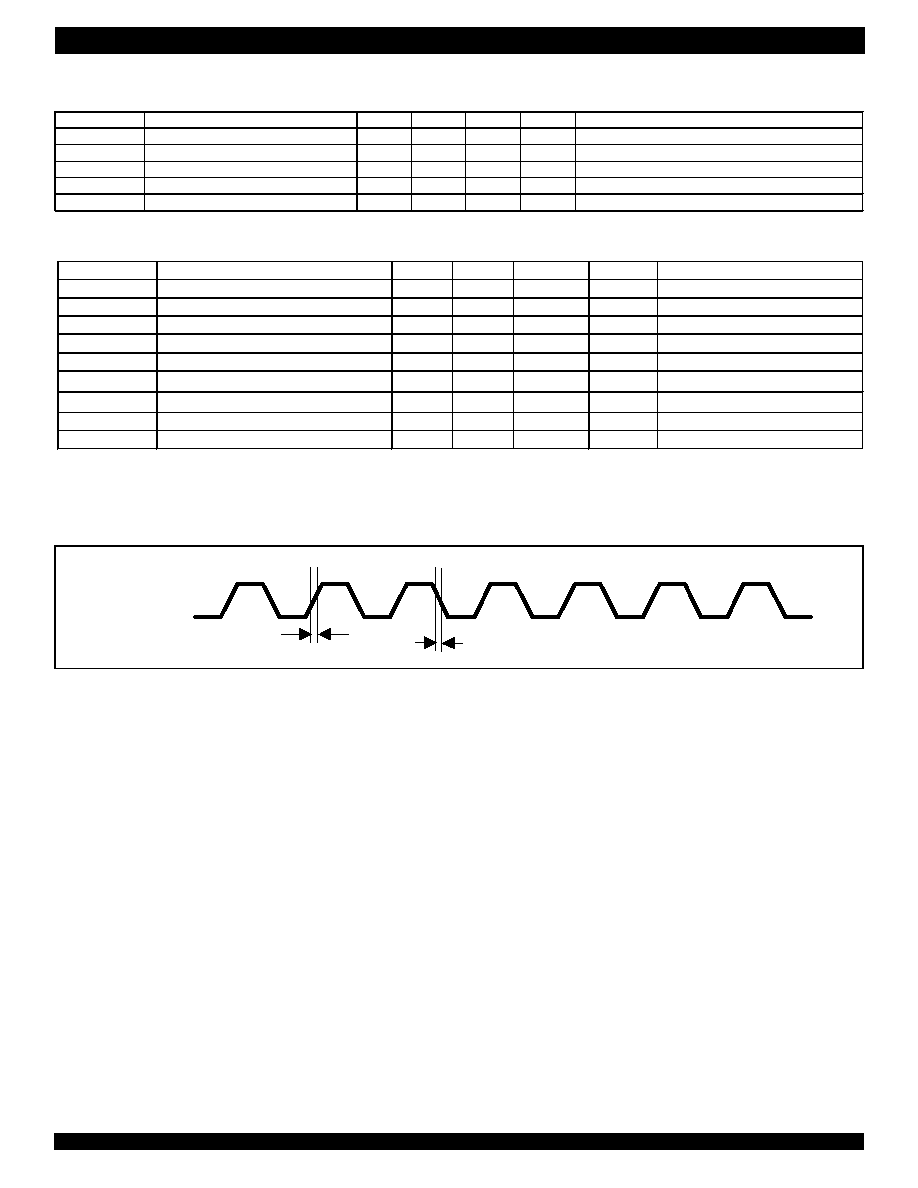

t4

MCLK

Figure 6. MCLK Timing

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT821054PQF

IC PCM CODEC QUAD MPI 64-PQFP

IDT82V3001APVG8

IC PLL WAN W/SGL REF INP 56-SSOP

IDT82V3010PVG

IC PLL WAN 51/E1/OC3 DUAL 56SSOP

IDT82V3011PVG

IC PLL WAN T1/E1/OC3 SGL 56-SSOP

IDT82V3012PVG8

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

IDT82V3155PVG

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

IDT82V3202NLG

IC PLL WAN EBU SGL 68-VFQFPN

IDT82V3255TFG

IC PLL WAN SMC STRATUM 3 64-TQFP

相关代理商/技术参数

IDT821054

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

IDT821054A

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

IDT821054APF

功能描述:IC PCM CODEC QUAD MPI 64-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)

IDT821054APF8

功能描述:IC PCM CODEC QUAD MPI 64-TQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)

IDT821054APFG

功能描述:IC PCM CODEC QUAD MPI 64-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)

IDT821054APFG8

功能描述:IC PCM CODEC QUAD MPI 64-TQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)

IDT821054PQF

功能描述:IC PCM CODEC QUAD MPI 64-PQFP RoHS:否 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)

IDT821054PQFG

功能描述:IC PCM CODEC QUAD MPI 64-PQFP RoHS:是 类别:集成电路 (IC) >> 接口 - 编解码器 系列:- 标准包装:2,500 系列:- 类型:立体声音频 数据接口:串行 分辨率(位):18 b ADC / DAC 数量:2 / 2 三角积分调变:是 S/N 比,标准 ADC / DAC (db):81.5 / 88 动态范围,标准 ADC / DAC (db):82 / 87.5 电压 - 电源,模拟:2.6 V ~ 3.3 V 电压 - 电源,数字:1.7 V ~ 3.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘 供应商设备封装:48-TQFN-EP(7x7) 包装:带卷 (TR)